- 您现在的位置:买卖IC网 > Sheet目录362800 > EVAL-AD1958EB (Analog Devices, Inc.) PLL/Multibit DAC

REV. 0

–3–

AD1958

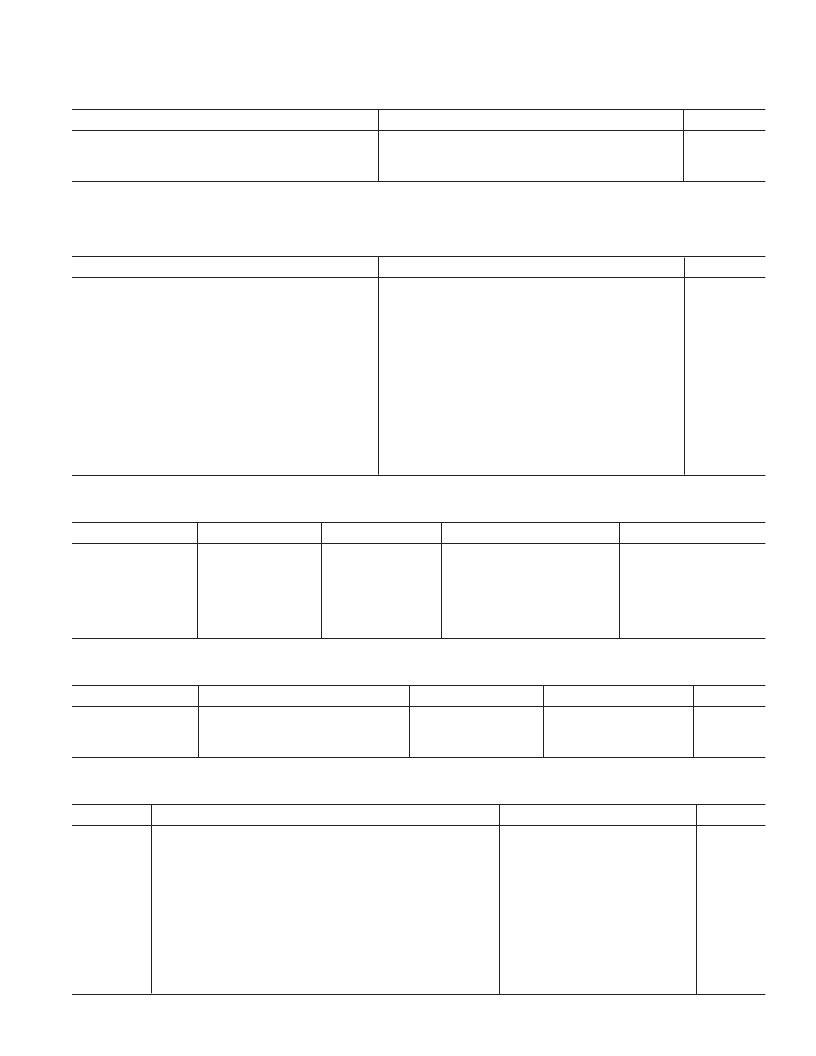

TEMPERATURE RANGE

Min

Typ

Max

Unit

°

C

°

C

°

C

Specifications Guaranteed

Functionality Guaranteed

Storage

25

–40

–55

+105

*

+125

NOTE

*

105

°

C ambient guaranteed for a 4-layer board, two 1 oz. planes, two 2 oz. signal layers. Derate to 85

°

C for 2-layer board, 2 oz. layers.

Specifications subject to change without notice.

POWER

Min

Typ

Max

Unit

Supplies

Voltage, Analog Digital PLL

Analog Current

Digital Current

PLL Current

Dissipation

Operation—All Supplies

Operation—Analog Supply

Operation—Digital Supply

Operation—PLL Supply

Power Supply Rejection Ratio

1 kHz 300 mV p-p Signal at Analog Supply Pins

20 kHz 300 mV p-p Signal at Analog Supply Pins

4.50

5

36

25

30

5.50

41

29

34

V

mA

mA

mA

455

180

125

150

540

mW

mW

mW

mW

–60

–50

dB

dB

Specifications subject to change without notice.

DIGITAL FILTER CHARACTERISTICS

Sample Rate (kHz)

Pass Band (kHz)

Stop Band (kHz)

Stop Band Attenuation (dB)

Pass Band Ripple (dB)

±

0.0002

±

0.0002

±

0.0005

0/–0.04 (DC–21.8 kHz)

0/–0.5 (DC–65.4 kHz)

0/–1.5 (DC–87.2 kHz)

44.1

48

96

192

DC–20

DC–21.8

DC–39.95

DC–87.2

24.1–328.7

26.23–358.28

56.9–327.65

117–327.65

75

75

75

60

Specifications subject to change without notice.

GROUP DELAY

Chip Mode

INT8

×

Mode

INT4

×

Mode

INT2

×

Mode

Group Delay Calculation

f

S

48 kHz

96 kHz

192 kHz

Group Delay

Unit

μ

s

μ

s

μ

s

24.625/f

S

15.75/f

S

14/f

S

513

164

72.91

Specifications subject to change without notice.

DIGITAL TIMING (Guaranteed over –40

°

C to +105 C, AVDD = DVDD = PVDD = 5.0 V 10%)

Min

Unit

t

DMP

t

DML

t

DMH

t

DBH

t

DBL

t

DBP

t

DLS

t

DLH

t

DDS

t

DDH

t

RSTL

MCLK Period (FMCLK = 256

×

FLRCLK)

MCLK LO Pulsewidth (All Modes)

MCLK HI Pulsewidth (All Modes)

BCLK HI Pulsewidth

BCLK LO Pulsewidth

BCLK Period

LRCLK Setup

LRCLK Hold (DSP Serial Port Mode Only)

SDATA Setup

SDATA Hold

RST LO Pulsewidth

54

15

10

20

20

60

20

20

15

15

15

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Specifications subject to change without notice.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

EVAL-AD1959EB

PLL/Multibit DAC

EVAL-AD1974EB

4 ADC with PLL, 192 kHz, 24-Bit Codec

EVAl-AD1974EBZ

4 ADC with PLL, 192 kHz, 24-Bit Codec

EVAL-AD1990EB

Audio Switching Amplifier

EVAL-AD1992EB

Audio Switching Amplifier

EVAL-AD1994EB

Audio Switching Amplifier

EVAL-AD421EB

Loop-Powered 4 mA to 20 mA DAC

Eval-AD5025EBZ

Fully Accurate 12-/14-/16-Bit VOUT DAC SPI Interface 2.7 V to 5.5 V in a TSSOP

相关代理商/技术参数

EVAL-AD1959EB

制造商:AD 制造商全称:Analog Devices 功能描述:PLL/Multibit DAC

EVAL-AD1970EB

制造商:Analog Devices 功能描述:EVAL BD BTSC ENCODER W INTEGRATED CODEC - Bulk

EVAL-AD1974AZ

功能描述:BOARD EVAL FOR AD1974 RoHS:是 类别:编程器,开发系统 >> 评估板 - 模数转换器 (ADC) 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- ADC 的数量:1 位数:12 采样率(每秒):94.4k 数据接口:USB 输入范围:±VREF/2 在以下条件下的电源(标准):- 工作温度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,软件

EVAL-AD1974EB

制造商:AD 制造商全称:Analog Devices 功能描述:4 ADC with PLL, 192 kHz, 24-Bit Codec

EVAL-AD1974EBZ

制造商:Analog Devices 功能描述:EVAL KIT FOR 4 ADC W/ PLL, 192 KHZ, 24BIT CODEC EVAL-AD1974E - Boxed Product (Development Kits)

EVAL-AD1990EB

制造商:Analog Devices 功能描述:EVAL BD CLASS D AUDIO POWER OUTPUT STAGE - Bulk

EVAL-AD1992EB

制造商:AD 制造商全称:Analog Devices 功能描述:Audio Switching Amplifier

EVAL-AD1994EB

制造商:Analog Devices 功能描述:EVAL BOARD FOR AD1994 - Bulk